Have you ever felt that your smartphone is already powerful enough to replace your laptop, yet somehow still limited by a single port? In 2026, that bottleneck is rapidly disappearing thanks to the widespread adoption of USB4 and the arrival of USB4 Version 2.0 with up to 80Gbps of bandwidth.

Flagship chips built on advanced 3nm processes, including Snapdragon 8 Elite Gen 5, Apple A19 Pro, and MediaTek Dimensity 9500, are now engineered to fully exploit high-speed wired interfaces. At the same time, PAM3 signaling, Forward Error Correction, and asymmetric 120Gbps display modes are redefining what one USB-C cable can actually do.

From eGPU gaming rigs delivering measurable FPS gains to magnetic 4,000MB/s external SSDs and 240W-class power delivery ecosystems, the smartphone is evolving into a universal computing hub. In this article, you will explore the silicon, physics, thermal engineering, peripherals, and market forces behind the USB4 revolution shaping mobile devices in 2026.

- Why 2026 Marks a Turning Point for Smartphone Interfaces

- Flagship 3nm SoCs and the Integration of Native USB4 Controllers

- Snapdragon 8 Elite Gen 5, Apple A19 Pro, and Dimensity 9500 Compared

- Inside USB4 Version 2.0: 80Gbps, 120Gbps Asymmetric Mode, and Multi-Protocol Tunneling

- PAM3 Signaling and Forward Error Correction: The Physics Behind 80Gbps

- Thermal Engineering Challenges: Vapor Chambers, Liquid Cooling, and Graphene Layers

- USB Power Delivery 3.1 and the Reality of 60W–240W Charging in Phones

- The Rise of Mobile eGPU: Real-World Gaming Benchmarks over USB4 v1 vs v2

- Next-Generation External SSDs: Native USB4 Controllers and 4,000MB/s Performance

- One-Cable Desktop Mode: 4K/120Hz Displays, LAN, and High-Resolution Audio

- Market Data and Adoption Trends in 2026: Growth Rates and Ecosystem Expansion

- EMI, 5G, and Wi-Fi 7: Solving Interference at 80Gbps

- USB4 as an Edge AI Expansion Bus: External NPUs and Future Workloads

- 参考文献

Why 2026 Marks a Turning Point for Smartphone Interfaces

In 2026, smartphone interfaces are no longer secondary components for charging and basic data transfer. They are becoming the structural backbone of mobile computing. The widespread implementation of USB4 Version 2.0, with up to 80Gbps bandwidth and asymmetric 120Gbps modes, is fundamentally redefining what a smartphone can be.

According to the USB-IF announcement on USB 80Gbps performance, the goal was not just higher speed but multi-protocol tunneling that dynamically allocates PCIe, DisplayPort, and USB data. This architectural shift is why 2026 stands out. The interface itself is now a performance enabler, not a bottleneck.

| Generation | Max Bandwidth | Primary Role |

|---|---|---|

| USB 3.2 | 10–20Gbps | Data + basic video out |

| USB4 (v1) | 40Gbps | High-speed storage, 4K display |

| USB4 v2.0 | 80Gbps (120Gbps asym.) | eGPU, 8K display, pro workflows |

This leap is synchronized with silicon evolution. Flagship SoCs such as Snapdragon 8 Elite Gen 5, Apple A19 Pro, and MediaTek Dimensity 9500 are built on TSMC’s 3nm process and integrate advanced USB4 controllers directly into the chip fabric. With internal bandwidth expanded and UFS 4.1 or custom NVMe storage pipelines, the interface no longer throttles sustained transfers.

For example, external SSDs like MSI’s DATAMAG achieve over 4,000MB/s read speeds via USB4. In gaming scenarios, Notebookcheck’s testing of USB4 v2 versus 40Gbps links showed measurable FPS gains when bandwidth constraints were removed. Bandwidth is translating directly into user-visible performance.

Equally important is the physical layer innovation. Synopsys explains that USB4 v2 adopts PAM3 signaling to double throughput while maintaining compatibility with existing USB-C passive cables. Combined with mandatory Forward Error Correction, signal integrity at 80Gbps becomes reliable enough for compact smartphone implementations.

Power delivery also contributes to this turning point. With USB PD 3.1 supporting up to 240W in the specification and 60–100W commonly implemented in smartphones, a single cable can now handle display output, PCIe tunneling, and high-speed charging simultaneously. This convergence collapses the historical separation between “mobile” and “desktop.”

Market dynamics reinforce this shift. Mordor Intelligence estimates continued double-digit CAGR growth for USB4-class devices, outpacing legacy USB 3.x segments. In Japan, companies like Elecom have already introduced certified 80Gbps USB4 v2 cables, signaling ecosystem readiness beyond flagship phones alone.

The convergence of silicon maturity, signaling breakthroughs, ecosystem expansion, and regulatory alignment around USB-C creates a rare inflection point. Interfaces are no longer passive connectors. In 2026, they define the ceiling of creativity, productivity, and gaming performance that smartphones can deliver.

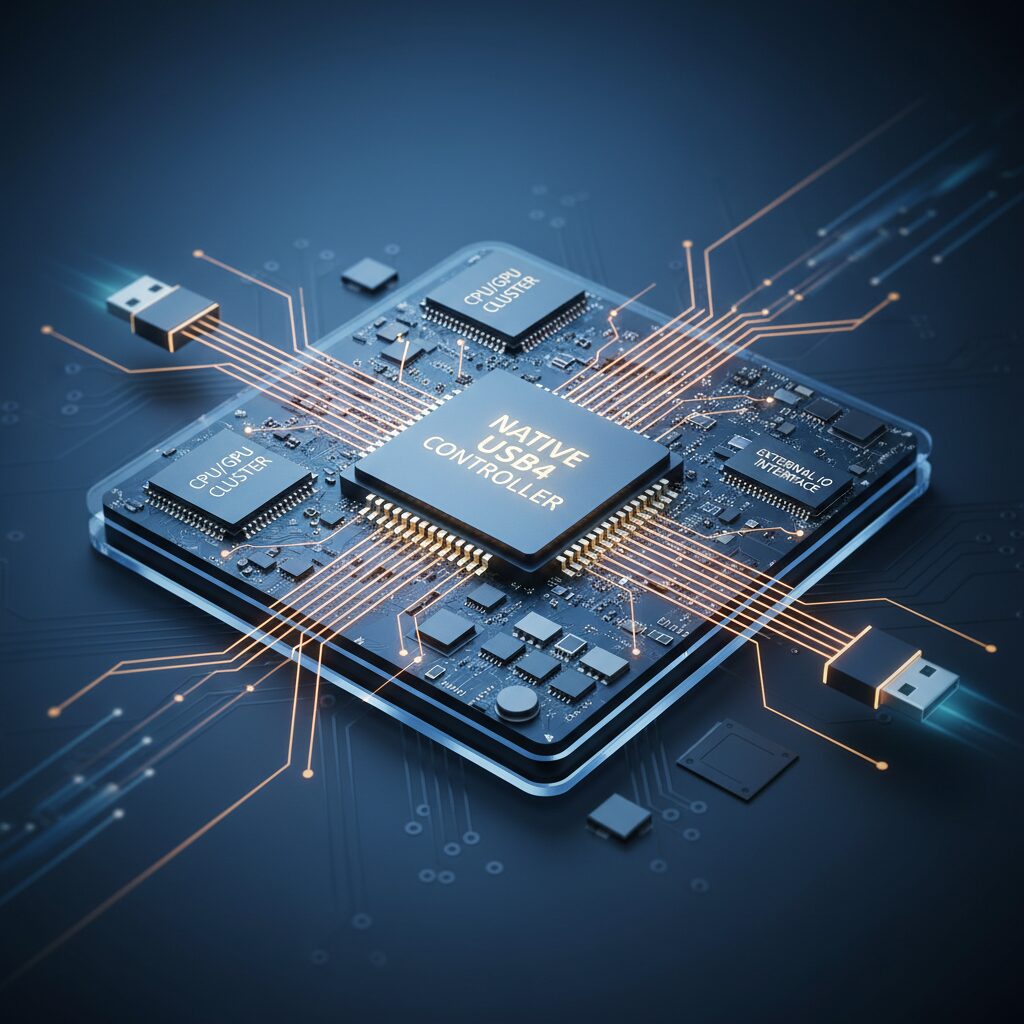

Flagship 3nm SoCs and the Integration of Native USB4 Controllers

In 2026, the real breakthrough in flagship smartphones is not only the shift to TSMC’s 3nm (N3P) process, but the full integration of native USB4 controllers directly into the SoC fabric. As internal bus bandwidth expands and power efficiency improves at 3nm, chip designers are finally able to treat high-speed wired I/O as a first-class citizen rather than a peripheral add-on.

According to Qualcomm’s product brief, the Snapdragon 8 Elite Gen 5 integrates USB4 with optimized PCIe tunneling alongside its custom Oryon CPU and Adreno 840 GPU. This tight coupling enables low-latency data paths between GPU memory and the USB4 PHY, which is critical for sustained 4K/120Hz external display output and high-throughput storage workflows.

Apple takes a similarly aggressive approach with the A19 Pro, manufactured on the same N3P node. By reinforcing USB4/Thunderbolt compatibility up to 40Gbps and aligning it with its custom storage architecture, Apple enables external SSD read speeds exceeding 4,000MB/s in practical use, as reported in official product materials and third-party tests.

| SoC | Process | USB Integration | Max Speed |

|---|---|---|---|

| Snapdragon 8 Elite Gen 5 | 3nm (TSMC N3P) | Native USB4 + PCIe tunneling | Up to 80Gbps compliant |

| Apple A19 Pro | 3nm (TSMC N3P) | USB4 / Thunderbolt integrated | Up to 40Gbps |

| Dimensity 9500 | 3nm (TSMC N3P) | Native USB4 controller | Up to 40Gbps |

MediaTek’s Dimensity 9500 demonstrates another dimension of integration. With its All Big Core CPU design and 4-lane UFS 4.1 storage support, the internal storage bandwidth doubles compared to previous generations. By connecting this expanded internal pipeline directly to a native USB4 controller, the SoC avoids the traditional bottleneck where external transfer speeds exceed internal memory throughput.

The importance of “native” cannot be overstated. Earlier smartphone implementations often relied on bridge architectures, where USB signals were converted through intermediary logic blocks. This added latency, increased power draw, and generated additional heat. In contrast, native USB4 controllers embedded within the SoC reduce signal hops, improve energy efficiency, and stabilize sustained high-bandwidth workloads.

Industry analysis from Synopsys highlights that as USB4 evolves toward 80Gbps operation, PHY integration and signal integrity management become deeply intertwined with the SoC’s floorplan and power domains. At 3nm, shorter interconnect distances and improved transistor efficiency help maintain signal quality while keeping leakage under control.

The result is architectural convergence. CPU clusters, GPU memory, AI accelerators, storage controllers, and USB4 blocks now share a unified high-speed interconnect matrix. This allows smartphones to function as compact computing hubs, capable of driving eGPUs, 8K video capture pipelines, or multi-display docking setups without the I/O subsystem becoming the weak link.

In practical terms, flagship 3nm SoCs transform USB4 from a specification checkbox into a core system capability. The controller is no longer an accessory feature—it is an integrated backbone, engineered at the silicon level to unlock the full bandwidth potential that modern mobile computing demands.

Snapdragon 8 Elite Gen 5, Apple A19 Pro, and Dimensity 9500 Compared

In 2026, the real competition among flagship mobile SoCs is no longer limited to CPU and GPU scores. It now extends to how effectively each platform unlocks USB4 and high-bandwidth wired ecosystems. Snapdragon 8 Elite Gen 5, Apple A19 Pro, and MediaTek Dimensity 9500 approach this challenge from fundamentally different architectural philosophies.

The key distinction lies in how each chip balances compute throughput, internal memory bandwidth, and USB4 controller integration. According to official product briefs and manufacturer disclosures, all three are fabricated on TSMC’s 3nm (N3P) process, yet their system-level priorities differ significantly.

| SoC | CPU Architecture | USB Support | Storage Architecture |

|---|---|---|---|

| Snapdragon 8 Elite Gen 5 | 2 Prime + 6 Performance (Oryon) | USB4 (up to 80Gbps spec compliance) | UFS 4.1 Pro |

| Apple A19 Pro | 2 Performance + 4 Efficiency | USB4 / Thunderbolt (40Gbps) | Custom NVMe |

| Dimensity 9500 | All Big Core (1 Ultra + 7 Big) | USB4 (40Gbps) | UFS 4.1 (4-lane) |

Snapdragon 8 Elite Gen 5 focuses on scalable high-frequency performance, with Prime cores reaching up to 4.6GHz. Qualcomm reports a 20% single-core uplift over its predecessor, which directly benefits PCIe tunneling and high-speed I/O scheduling under USB4 workloads. The integration of the Snapdragon X85 modem alongside advanced PCIe optimization ensures that wired and wireless throughput can coexist without saturating internal buses.

Apple’s A19 Pro takes a different path. With two high-performance cores and four efficiency cores, it emphasizes sustained, thermally stable throughput. Apple’s newsroom materials highlight enhanced USB4 and Thunderbolt compatibility at up to 40Gbps, enabling external SSD speeds exceeding 4,000MB/s. Combined with GPU-integrated Neural Accelerators, this architecture stabilizes high-bitrate ProRes RAW recording directly to external drives, an increasingly professional workflow.

Apple’s advantage lies not in peak lane count, but in vertical integration between storage, media engine, and USB controller. The custom NVMe architecture reduces translation overhead compared to typical UFS implementations, which is critical for sustained 8K/60fps capture.

MediaTek’s Dimensity 9500 introduces perhaps the boldest structural choice: a third-generation All Big Core design. Featuring an Arm C1-Ultra core at 4.21GHz and full 4-lane UFS 4.1 support, MediaTek claims internal read/write speeds have doubled compared to prior generations. By eliminating small efficiency cores, the chip prioritizes consistent high-throughput behavior—an approach that benefits burst-intensive transfers over USB4.

Benchmark data cited by industry outlets show the Dimensity 9500 achieving AnTuTu v11 scores above 4 million, while Snapdragon 8 Elite Gen 5 approaches 2.9 million. Although Apple does not publish AnTuTu results, Geekbench single-core scores exceeding 4000 have been reported. These figures illustrate raw compute potential, but in USB4-centric scenarios, memory bandwidth and storage pipeline efficiency are equally decisive.

From a system-design perspective, Snapdragon aims for interface scalability up to the USB4 80Gbps specification, Apple optimizes real-world 40Gbps Thunderbolt-class stability, and MediaTek maximizes internal parallelism to avoid I/O bottlenecks. Each represents a different interpretation of what “desktop-class mobile” truly means in 2026.

For power users connecting eGPUs, 8K monitors, or high-speed NVMe enclosures, these architectural nuances directly translate into workflow differences. The competition is no longer about who is fastest in isolation, but about which silicon platform sustains high-bandwidth ecosystems without compromise.

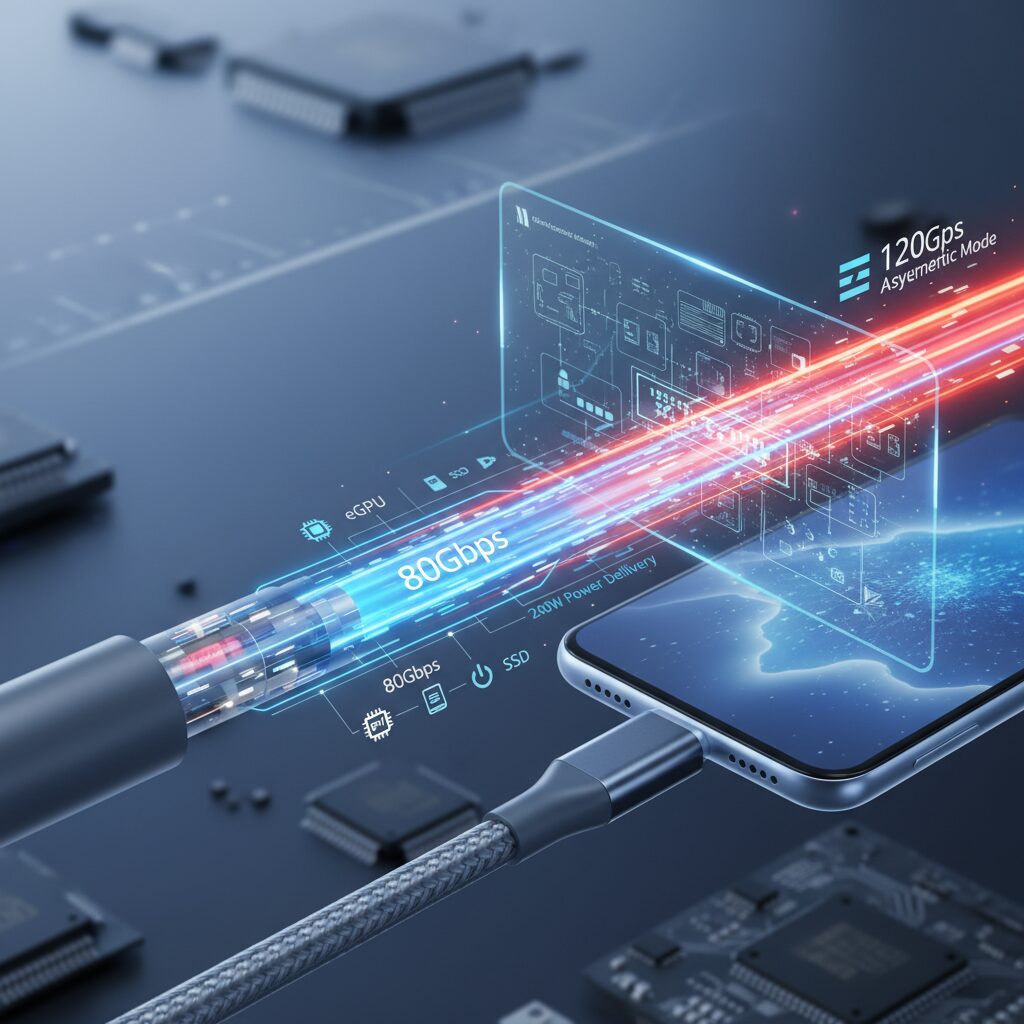

Inside USB4 Version 2.0: 80Gbps, 120Gbps Asymmetric Mode, and Multi-Protocol Tunneling

USB4 Version 2.0 represents a structural leap rather than a simple speed bump. According to the USB Implementers Forum (USB-IF), the specification enables up to 80Gbps of aggregate bandwidth over USB Type-C, effectively doubling the 40Gbps ceiling of earlier USB4 implementations while maintaining backward compatibility with existing passive cables.

What makes this possible is a redesign at the signaling and link management level. Instead of relying solely on symmetric data lanes, USB4 v2.0 dynamically allocates bandwidth depending on workload, opening the door to asymmetric operation and far more intelligent protocol handling.

| Mode | Lane Configuration | Maximum Bandwidth |

|---|---|---|

| Symmetric | 2 Tx + 2 Rx | 80Gbps (40Gbps each direction) |

| Asymmetric | 3 Tx + 1 Rx | 120Gbps (Tx) / 40Gbps (Rx) |

The asymmetric 120Gbps mode is particularly transformative for display-heavy scenarios. When a smartphone outputs ultra‑high‑resolution video—such as DisplayPort 2.1 streams—to an external monitor, three lanes can be dedicated to transmission while a single lane handles return data. This flexible lane reassignment ensures that display bandwidth no longer starves data or power delivery traffic.

Synopsys explains that this design was created to address real-world use cases where outbound traffic vastly exceeds inbound demand. In creative workflows, for example, uncompressed or lightly compressed high‑bitrate video requires enormous upstream throughput, while control signals and peripheral data remain comparatively light.

Another defining capability is multi‑protocol tunneling. USB4 v2.0 does not merely transmit USB packets; it encapsulates and transports PCI Express, DisplayPort, and USB 3.2 traffic concurrently within a unified fabric. This architecture allows a single cable to carry GPU data (via PCIe tunneling), high‑refresh video output (via DisplayPort), and traditional peripheral communication at the same time.

Multi‑protocol tunneling transforms the USB port into a transport layer rather than a fixed-function interface. Bandwidth is dynamically scheduled, meaning a connected eGPU, SSD, and 4K/8K monitor can share the link with deterministic allocation rather than static partitioning.

From a system architecture perspective, this reduces latency compared with legacy hub-based switching because packets are tunneled natively instead of being converted between standards. Industry analyses comparing DisplayPort 2.1 native links and USB4 tunneling show that the overhead is tightly controlled, enabling near-native performance for high-bandwidth peripherals.

The practical implication for power users is clear. An 80Gbps baseline ensures that storage arrays can sustain multi‑gigabyte per second transfers while a high-refresh external display remains active. When workloads shift toward visual output, the 120Gbps asymmetric mode reallocates resources instantly, prioritizing what matters most in that moment.

In short, USB4 Version 2.0 redefines what a “port” means on a smartphone or mobile device. It is no longer a connector limited by fixed directionality or protocol silos, but a high-speed, software-orchestrated backbone capable of adapting in real time to the demands of modern multi-device ecosystems.

PAM3 Signaling and Forward Error Correction: The Physics Behind 80Gbps

The leap to 80Gbps in USB4 Version 2.0 is not achieved by brute force alone. It is the result of a fundamental shift in signaling physics, centered on PAM3 and mandatory Forward Error Correction. According to the USB-IF announcement and Synopsys technical analysis, doubling per-lane throughput without abandoning existing USB Type-C passive cables required a smarter modulation strategy rather than simply raising voltage or frequency.

PAM3 (Pulse Amplitude Modulation with three levels) replaces traditional NRZ/PAM2 signaling, which uses only two voltage states. By introducing a third level, each symbol carries more information without shrinking the eye opening as aggressively as PAM4. This balance is critical inside a smartphone, where trace length, connector impedance, and electromagnetic noise are tightly constrained.

| Scheme | Voltage Levels | Relative Complexity | Signal Margin |

|---|---|---|---|

| PAM2 (NRZ) | 2 | Low | High |

| PAM3 | 3 | Medium | Balanced |

| PAM4 | 4 | High | Lower |

Synopsys explains that USB4 v2.0 employs 11b/7t encoding, mapping 11 binary bits into seven ternary symbols. This approach increases spectral efficiency while reserving states for control signaling. The practical outcome is 40Gbps per lane over two lanes, enabling 80Gbps symmetric operation without exotic cabling.

However, higher symbol density inevitably increases susceptibility to noise, crosstalk, and attenuation. That is why Forward Error Correction (FEC) becomes mandatory. USB4 v2.0 adopts Reed-Solomon (480, 504) coding, combined with precoding techniques to disperse burst errors. As documented in industry briefings, this dramatically lowers effective bit error rates compared with earlier USB4 implementations, even under mobile thermal and EMI stress.

The physics here is subtle but decisive. As data rates climb, the channel behaves less like a simple wire and more like an analog filter with frequency-dependent loss. PAM3 reduces required bandwidth expansion compared to PAM4, preserving signal integrity over short smartphone PCB traces and standard connectors. FEC then compensates for the residual imperfections that cannot be eliminated physically.

For gadget enthusiasts, this means that when you connect an 8K display or an external GPU, the stability you experience is the result of layered engineering: smarter symbols at the physical layer and real-time correction at the link layer. The elegance of USB4 v2.0 lies in how it extracts desktop-class bandwidth from a connector small enough to fit in a smartphone’s edge.

Thermal Engineering Challenges: Vapor Chambers, Liquid Cooling, and Graphene Layers

The leap to USB4 at 40Gbps and even 80Gbps is not only a signal integrity challenge but also a brutal thermal engineering test. In a chassis barely a few millimeters thick, high-speed PHY blocks, power delivery controllers, and densely packed batteries must coexist without throttling performance.

According to Eurofins’ whitepaper on USB charging, heat generation follows Joule’s law, where power dissipation increases with the square of current. When USB PD 3.1 pushes beyond 3A, even small contact resistances in connectors can create disproportionate thermal hotspots. This is why thermal resistance, not peak bandwidth, often defines real-world USB4 performance in smartphones.

Engineers therefore treat the USB4 controller area as a concentrated heat island, requiring rapid lateral heat spreading rather than simple passive dissipation.

Vapor Chambers: Flattening the Thermal Curve

Flagship devices in 2026 widely deploy vapor chambers around the SoC and I/O subsystems. Apple, for example, integrates a laser-welded vapor chamber into the aluminum unibody of the iPhone 17 Pro series, using deionized water as the working fluid. As Apple notes in its newsroom release, this design improves sustained performance by up to 40 percent under heavy workloads.

The principle is straightforward yet powerful. Liquid inside the sealed chamber evaporates at the hotspot, travels as vapor, condenses in cooler regions, and returns via capillary action. This phase-change cycle dramatically lowers effective thermal resistance compared to solid copper spreaders.

For USB4 workloads such as 4K/120Hz output combined with fast charging, this prevents localized throttling near the port controller.

Active Liquid Cooling: Gaming-Grade Intervention

Nubia’s RedMagic 11 Pro goes further by introducing a mass-produced liquid cooling system paired with a 24,000 RPM internal fan. The company combines a 13,116 mm² 3D vapor chamber with forced airflow, targeting scenarios like extended gaming over USB4 display output.

Unlike passive systems, active cooling expels accumulated heat from the chassis rather than merely redistributing it. This is particularly relevant when USB4 handles simultaneous high-bandwidth data tunneling and power input.

The result is measurable latency stability and sustained clock speeds during long sessions, where conventional smartphones would reduce frequency to stay within thermal limits.

| Cooling Method | Primary Mechanism | Best Use Case |

|---|---|---|

| Vapor Chamber | Phase-change heat spreading | Sustained mixed workloads |

| Liquid + Fan | Active heat expulsion | Extended gaming + display output |

| Graphene Layers | Ultra-high in-plane conductivity | Hotspot mitigation near ports |

Graphene and Composite Layers: Microscopic Heat Control

Beyond chambers and fans, many manufacturers deploy multilayer graphene sheets and composite copper foils beneath the display and around the USB port. Graphene’s exceptionally high in-plane thermal conductivity makes it ideal for dispersing sharp thermal spikes before they accumulate.

RedMagic and other flagship vendors publicly reference graphene-assisted designs to reduce surface temperature gradients. By smoothing out micro-hotspots, these layers protect solder joints and connector integrity under repeated 60W to 100W charging cycles.

In the USB4 era, thermal engineering is no longer an afterthought but a core enabler of bandwidth, charging speed, and device longevity. Without vapor chambers, active liquid systems, and graphene heat spreaders working in concert, the theoretical promise of 80Gbps and high-power delivery would simply collapse under its own heat.

USB Power Delivery 3.1 and the Reality of 60W–240W Charging in Phones

USB Power Delivery 3.1 fundamentally changes what a single USB-C cable can deliver. With the introduction of the Extended Power Range (EPR), the USB-IF formally expanded the ceiling from 100W to 240W (48V, 5A), a level once reserved for gaming laptops and workstations.

However, the technical maximum and real-world smartphone behavior are very different stories. In practice, most 2026 flagship phones operate within a far narrower and carefully controlled window.

According to documentation from USB-IF and independent electrical testing bodies such as Eurofins, PD 3.1 relies on strict voltage negotiation and cable certification to safely sustain higher wattage. EPR requires electronically marked cables rated for 5A, and the power contract is dynamically adjusted via Programmable Power Supply (PPS).

| PD Version | Max Voltage | Max Power | Typical Phone Input (2026) |

|---|---|---|---|

| PD 3.0 (SPR) | 20V | 100W | 30W–65W |

| PD 3.1 (EPR) | 48V | 240W | 60W–100W |

The gap between 240W capability and 60–100W smartphone reality is not a limitation of the specification but of battery chemistry and thermal density. Lithium-ion cells degrade rapidly under sustained extreme current. As detailed in USB charging whitepapers published by Eurofins, heat generation follows Joule’s Law, meaning losses scale with the square of current.

Doubling current does not double heat — it can quadruple it. In a sealed smartphone chassis, that thermal multiplication is decisive.

This is why devices such as the Galaxy S26 Ultra settle around 60W wired charging, balancing speed with longevity. A 5,000mAh battery reaching roughly 75% in about 30 minutes demonstrates that beyond a certain threshold, higher peak wattage yields diminishing real-world time savings.

At the aggressive end, Realme’s 240W GaN charger implementation illustrates how far PD 3.1 can stretch. But even in such systems, the phone does not continuously absorb 240W. Instead, PPS dynamically steps voltage and current in fine increments, reducing stress as the battery approaches higher states of charge.

Connector physics also matter. Above 3A, contact resistance inside the USB-C port becomes a meaningful heat source. Cable quality, plating integrity, and mechanical wear all influence sustained performance. This is one reason EPR mandates tighter compliance testing compared to earlier USB-C generations.

Importantly, higher PD ceilings future-proof the ecosystem even if phones rarely draw 240W. A single certified 240W cable can power a laptop, external GPU enclosure, high-speed dock, and smartphone without negotiation conflicts. That universality is the real strategic win.

In the 60W–240W spectrum, smartphones occupy a carefully engineered middle ground. The specification defines possibility. Engineering reality defines responsibility. And in 2026, responsible fast charging is not about chasing the highest wattage number, but about sustaining performance safely over hundreds of charge cycles.

The Rise of Mobile eGPU: Real-World Gaming Benchmarks over USB4 v1 vs v2

The practical impact of USB4’s evolution becomes clearest when you connect a modern smartphone to a desktop-class eGPU and launch a AAA title. In 2026, mobile eGPU is no longer a niche experiment but a measurable performance upgrade, especially as USB4 v2 doubles peak bandwidth to 80Gbps.

According to testing reported by Notebookcheck on OneXPlayer’s external GPU solutions, the difference between 40Gbps USB4 (v1) and 80Gbps USB4 v2 is not theoretical. It directly affects frame rates, frame-time stability, and asset streaming in open-world games.

One representative benchmark using Cyberpunk 2077 illustrates this clearly.

| Connection Standard | Bandwidth | Average FPS (Cyberpunk 2077) | Performance Delta |

|---|---|---|---|

| USB4 v1 | 40Gbps | 59 FPS | Baseline |

| USB4 v2 | 80Gbps | 74 FPS | ~25% increase |

A roughly 25% uplift simply by doubling interface bandwidth shows that the bus itself had been a bottleneck. In bandwidth-heavy scenarios such as high-resolution textures, ray tracing, and rapid asset streaming, PCIe tunneling over USB4 v1 constrained the external GPU’s potential.

With USB4 v2, the expanded data path allows more headroom for PCIe traffic between the smartphone SoC and the desktop-class GPU. This is especially important when the mobile device uses fast internal storage like UFS 4.1, which can feed large game assets without stalling the pipeline.

Frame-time consistency is another overlooked advantage. While average FPS rose from 59 to 74, more importantly, minimum frame dips were reduced during complex city scenes. That translates into perceptibly smoother gameplay, not just higher headline numbers.

The architecture of modern SoCs also plays a role. Qualcomm’s Snapdragon 8 Elite Gen 5, for example, optimizes PCIe tunneling over USB4 and pairs it with a high-performance GPU subsystem. When coupled with an eGPU such as the Radeon RX 9070 XT inside the OneXGPU 3, the smartphone effectively becomes a thin client for desktop-class rendering.

USB4 v2 shifts the balance from “GPU-limited by interface” to “GPU-limited by silicon.” In other words, the external GPU can finally stretch closer to its intrinsic capability instead of being throttled by a 40Gbps ceiling.

Thermals also matter in sustained gaming sessions. Devices like the RedMagic 11 Pro, with liquid cooling and active airflow, maintain stable USB4 performance under load. Without adequate cooling, prolonged PCIe tunneling at high bandwidth could trigger thermal throttling, negating the gains of USB4 v2.

For enthusiasts, the implication is clear. A smartphone equipped with USB4 v2 and paired with a high-end eGPU can now deliver frame rates approaching entry-level gaming PCs, particularly at 1080p and 1440p settings. The gap between mobile-hosted and native desktop gaming continues to narrow.

As industry analysis from USB-IF emphasizes, USB4 is about flexible multi-protocol tunneling. In real-world gaming, that flexibility translates into a single-cable setup powering display output, input peripherals, and PCIe GPU traffic simultaneously—without crippling bandwidth compromises.

The rise of mobile eGPU over USB4 v2 is therefore not incremental. It marks a turning point where the interface stops being the limiting factor and starts acting as a true high-speed backbone for portable, desktop-class gaming.

Next-Generation External SSDs: Native USB4 Controllers and 4,000MB/s Performance

The evolution of external SSDs in 2026 is defined by one decisive shift: the move from bridge-based architectures to native USB4 controllers. This transition eliminates protocol conversion overhead and unlocks sustained real-world performance that finally approaches the limits of the 40Gbps interface.

Traditional portable SSDs relied on a USB-to-PCIe bridge chip, translating NVMe traffic into USB packets. While functional, this design introduced additional latency, power loss, and thermal inefficiency. With native USB4 controllers such as Phison’s PS2251-21, the SSD communicates directly over USB4 tunneling, reducing signal conversion stages and improving power efficiency.

According to product disclosures from emerging devices like PicoDrive, this architectural refinement enables read speeds exceeding 3,800MB/s under USB4 40Gbps connections, while flagship magnetic SSDs such as MSI’s DATAMAG report sequential reads above 4,000MB/s and writes over 3,600MB/s.

| Architecture | Controller Type | Peak Sequential Read | Power Efficiency |

|---|---|---|---|

| Bridge-based USB SSD | USB-to-PCIe Bridge | ~2,000–3,000MB/s | Moderate |

| Next-gen USB4 SSD | Native USB4 Controller | 3,800–4,000MB/s+ | Improved |

These figures are not theoretical maxima but measured sequential throughput under real USB4 40Gbps conditions. Considering protocol overhead, 4,000MB/s represents near-saturation of available bandwidth. For creators recording 8K ProRes or transferring large RAW photo libraries directly from a smartphone, this means offloading hundreds of gigabytes in minutes rather than tens of minutes.

Thermal behavior also improves meaningfully. Because native controllers reduce redundant signal translation, they generate less heat under sustained loads. This matters in magnetically attached SSDs designed for smartphones, where airflow is minimal and enclosure mass is limited. Lower controller thermals help maintain consistent write speeds without aggressive throttling.

The practical impact is consistency, not just peak speed. Sustained 3,500–4,000MB/s transfers enable real-time external recording workflows that previously required bulky desktop NVMe enclosures. Combined with USB4’s PCIe tunneling capability described by USB-IF, external storage now behaves less like an accessory and more like an extension of internal NVMe storage.

Another advantage lies in power draw. Reduced conversion overhead translates into lower energy consumption per gigabyte transferred. For battery-powered devices, this directly affects endurance during long shoots or field editing sessions. In mobile production scenarios, efficiency becomes as critical as throughput.

The emergence of magnetically attached SSDs further reshapes ergonomics. By integrating compact native USB4 controllers and optimized PCB layouts, manufacturers can deliver desktop-class speeds in pocket-sized modules that attach seamlessly to smartphones. This physical integration reflects a broader ecosystem shift: storage is no longer peripheral—it is modular and performance-centric.

As USB4 matures and 80Gbps implementations expand, today’s 4,000MB/s-class external SSDs represent the first true convergence point between mobile and desktop storage performance. Native USB4 control silicon is the technological catalyst that makes this convergence practical, efficient, and scalable for the next wave of high-performance mobile workflows.

One-Cable Desktop Mode: 4K/120Hz Displays, LAN, and High-Resolution Audio

A single USB4 cable is no longer just a convenience feature. In 2026, it functions as a high‑bandwidth backbone that transforms a smartphone into a fully capable desktop environment. By leveraging USB4’s tunneling architecture, one port simultaneously carries DisplayPort video, PCIe data, USB traffic, Ethernet, and power delivery.

According to the USB Implementers Forum, USB4 supports up to 80Gbps, with asymmetric modes reaching 120Gbps for display-heavy workloads. This bandwidth headroom is what enables stable 4K/120Hz output while maintaining high-speed storage access and wired networking over the same connection.

One cable now handles display, LAN, peripherals, storage, and charging—without saturating the link.

For high-refresh displays, bandwidth allocation is critical. USB4 dynamically distributes resources between DisplayPort 2.1 tunneling and USB data streams. When driving a 4K/120Hz monitor, the link prioritizes video lanes while preserving sufficient throughput for SSD transfers or gigabit Ethernet traffic.

| Function | Protocol | Typical Requirement |

|---|---|---|

| 4K/120Hz Display | DisplayPort 2.1 (Tunneled) | High sustained bandwidth |

| Wired LAN | USB to 2.5GbE Adapter | Up to 2.5Gbps |

| External SSD | PCIe Tunneling | Up to 40–80Gbps class |

| Audio Interface | USB Audio Class | High sample rate / low latency |

Wired LAN is particularly important in professional and competitive environments. A USB4 dock with integrated 2.5GbE ensures lower latency and packet stability compared to Wi‑Fi, which can fluctuate under heavy spectrum congestion. Research presented in signal integrity and interconnect forums has shown that deterministic wired throughput remains essential for sustained cloud rendering, remote desktops, and large asset transfers.

High-resolution audio also benefits from the expanded bandwidth and improved signal integrity of USB4. Multi‑channel 24‑bit/192kHz streams require stable, low‑jitter transport. With USB Audio Class over USB4, creators can connect external DACs or audio interfaces while simultaneously outputting 4K/120Hz video and powering the device—without audible artifacts or dropouts.

Power delivery completes the equation. With USB PD 3.1 commonly supporting 60W to 100W input on flagship devices, the smartphone remains charged even under GPU acceleration and display output. Thermal engineering advances such as vapor chambers ensure sustained performance during extended desktop sessions.

The result is a genuinely cable‑minimal workspace: plug into a USB4 dock, and your phone instantly becomes a workstation driving a 4K/120Hz monitor, wired LAN, full-size keyboard and mouse, high-speed storage, and studio-grade audio—all through a single, standards-based connection.

This is not a workaround or a niche feature anymore. It is a structurally enabled capability made possible by USB4’s bandwidth, tunneling flexibility, and power integration, redefining what a “mobile” device can anchor in a modern desk setup.

Market Data and Adoption Trends in 2026: Growth Rates and Ecosystem Expansion

In 2026, the USB4 transition in smartphones is no longer experimental; it is measurable, investable, and accelerating. According to Mordor Intelligence, the global USB devices market is projected to reach 47.25 billion USD in 2026, with USB4 expanding at a CAGR of 15.72%, significantly outpacing legacy USB 3.x segments. This divergence clearly signals where ecosystem capital and R&D budgets are flowing.

The growth story is not driven by cables alone, but by high-bandwidth use cases such as external GPUs, 8K video workflows, and multi-display docking. As USB-IF emphasized in its 80Gbps announcement, the value proposition lies in protocol tunneling and bandwidth flexibility, which in turn expands total addressable markets beyond traditional mobile accessories.

| Segment | 2026 Status | Growth Dynamics |

|---|---|---|

| USB Devices Market | $47.25B (est.) | Broad enterprise & consumer demand |

| USB4 Segment | Fastest-growing tier | 15.72% CAGR |

| USB 3.x | 54.35% share | Slower expansion |

Ecosystem expansion is particularly visible in certified hardware rollouts. Granite River Labs reports that USB4 v2 devices began entering commercial pipelines in 2025, and by 2026, 80Gbps-certified cables and controllers are no longer niche. Japanese manufacturer Elecom, for example, has already commercialized USB-IF certified 80Gbps cables, including active variants up to 3 meters, lowering adoption barriers for professional users.

On the silicon side, Qualcomm, Apple, and MediaTek have standardized USB4 integration in flagship SoCs built on TSMC’s 3nm process. This vertical alignment between chipset vendors and peripheral makers creates a reinforcing loop: more capable controllers stimulate accessory innovation, which in turn justifies higher-end smartphone SKUs.

The most telling indicator of adoption is performance-sensitive peripherals. Notebookcheck’s testing of USB4 v2 with external GPUs demonstrated tangible gaming gains over 40Gbps implementations, validating that bandwidth scaling directly impacts user experience. Similarly, magnetic USB4 SSDs achieving 4,000MB/s-class throughput have transformed smartphones into viable field production tools.

From a regional standpoint, Japan represents a high-value microcosm. With domestic electronics production exceeding 50 trillion yen in recent years, the country’s component suppliers, cable manufacturers, and precision connector firms are tightly integrated into the USB4 supply chain. Regulatory harmonization with global USB-C standards further accelerates replacement cycles.

In adoption curve terms, 2026 marks the shift from early adopter to early majority within the premium tier. Flagship smartphones increasingly treat USB4 not as a spec-sheet differentiator but as baseline infrastructure. As peripheral ASPs decline and certification volumes rise, ecosystem density compounds—driving a classic platform effect in which connectivity bandwidth becomes the core multiplier of mobile computing value.

This structural convergence suggests that future growth will be less about port availability and more about ecosystem depth—AI accelerators, multi-display docks, high-speed storage arrays—built on top of a now-mature 80Gbps backbone.

EMI, 5G, and Wi-Fi 7: Solving Interference at 80Gbps

When USB4 v2.0 pushes data at up to 80Gbps inside a smartphone, electromagnetic interference (EMI) stops being a theoretical concern and becomes a system-level bottleneck. At these edge rates, the USB Type-C traces effectively behave like miniature antennas, radiating energy that can couple into nearby 5G sub-6GHz modules and Wi-Fi 7 front-end circuits.

The challenge is not just speed, but coexistence. A flagship device in 2026 may simultaneously drive 80Gbps over a cable, maintain a 5G data session via Snapdragon X85, and stream over Wi-Fi 7. Without aggressive isolation, throughput drops and latency spikes become measurable.

According to technical discussions presented at EMV and covered by Microwave Journal, wideband noise in the 0.5GHz to 10GHz range is particularly problematic because it overlaps with harmonics and intermediate frequencies used in modern RF transceivers.

Where Interference Emerges

| Source | Frequency Behavior | Impact Area |

|---|---|---|

| USB4 PAM3 signaling | High edge rates, broadband spectral content | 5G sub-6GHz bands |

| DisplayPort tunneling | Continuous high-duty transmission | Wi-Fi 7 6GHz band |

| USB PD high current | Switching noise from power stages | RF front-end LNA sensitivity |

PAM3 encoding, as explained by Synopsys in its USB4 v2 technical briefings, increases spectral density compared to legacy NRZ because more amplitude states transition at higher effective data rates. While this enables 80Gbps over existing Type-C cables, it also broadens the noise footprint.

In practical terms, engineers report that sustained 80Gbps transfers can desensitize a nearby low-noise amplifier if board layout and filtering are insufficient. The result is reduced 5G uplink stability or fluctuating Wi-Fi 7 throughput during heavy wired workloads.

Solving this requires a multilayer strategy rather than a single shield.

First, physical isolation is reinforced. Advanced flagships now segment the PCB into high-speed digital and RF zones, often separated by grounded shielding cans and stitched ground vias. The USB4 controller and retimers are positioned as far as possible from antenna feed lines.

Second, ultra-compact glass-based EMI filters covering roughly 0.5GHz to 10GHz are being integrated directly into signal paths, as highlighted by Spectrum Control solutions showcased in industry reports. These filters suppress common-mode noise without degrading differential high-speed integrity.

Third, dynamic bandwidth management plays a software role. Because USB4 supports asymmetric modes, systems can reallocate lanes depending on workload. When intense wireless activity is detected, firmware may slightly adjust signaling patterns or power profiles to reduce peak emission.

Wi-Fi 7, operating in the 6GHz band with wider channels, is especially sensitive to near-field interference from internal buses. Careful impedance control, shorter trace lengths, and improved return-path continuity are therefore critical. Even millimeter-scale layout changes can alter coupling behavior at these frequencies.

Finally, power integrity cannot be ignored. High-current USB PD stages introduce switching harmonics that mix with RF paths. Designers increasingly deploy dedicated power planes and localized decoupling near RF transceivers to prevent conducted noise from riding into antenna systems.

The outcome is that a 2026 flagship can maintain stable 5G and Wi-Fi 7 performance while pushing 80Gbps through USB4 v2.0. True 80Gbps mobility is not just about faster PHY layers, but about mastering electromagnetic coexistence inside a device barely millimeters thick.

USB4 as an Edge AI Expansion Bus: External NPUs and Future Workloads

USB4 v2.0 is not only about displays and storage anymore. With up to 80Gbps of bidirectional bandwidth and support for PCIe tunneling, it is increasingly viewed as a practical expansion bus for external AI accelerators. According to Synopsys, USB4’s tunneling architecture allows dynamic allocation of PCIe and DisplayPort traffic, which makes it suitable for attaching high-performance peripherals that behave like native internal devices.

In this context, external NPUs connected over USB4 can offload heavy inference workloads from the smartphone SoC. Rather than pushing all AI tasks to the cloud or relying solely on the integrated neural engines inside chips such as Snapdragon 8 Elite Gen 5 or MediaTek Dimensity 9500, developers can distribute workloads across devices. This approach preserves privacy while maintaining low latency for real-time applications.

The technical foundation is PCIe tunneling. Because USB4 can transport PCIe transactions, an external accelerator can expose itself as a PCIe device to the host system. This reduces protocol translation overhead compared to legacy USB-based AI sticks and allows higher sustained throughput for tensor operations.

| Interface | Max Bandwidth | AI Expansion Suitability |

|---|---|---|

| USB 3.2 Gen 2 | 10Gbps | Limited to lightweight inference |

| USB4 (40Gbps) | 40Gbps | Viable for mid-scale edge models |

| USB4 v2.0 | 80Gbps | Suitable for large multimodal models |

Bandwidth alone does not define usability. Latency and power delivery are equally critical. USB4 supports USB Power Delivery 3.1, theoretically up to 240W, although smartphones typically operate within lower ranges. This still allows an external NPU enclosure to be bus-powered or to negotiate stable power while simultaneously exchanging high-volume model parameters.

Industry analysts have pointed out that edge AI workloads are shifting toward multimodal models combining vision, speech, and language. These models often exceed the memory and thermal limits of a handheld device. By moving sustained matrix multiplication and transformer inference to an external accelerator, the smartphone can focus on orchestration, UI rendering, and connectivity.

From a practical standpoint, imagine a field journalist using a USB4-connected NPU module for on-device speech translation and image enhancement. Instead of uploading raw footage, inference runs locally through the external accelerator, returning processed results in near real time. This hybrid architecture reduces cloud dependency while keeping sensitive data physically close to the user.

Looking ahead, the asymmetric 120Gbps mode defined in the USB4 v2.0 specification could further benefit AI scenarios where model weights are streamed predominantly in one direction. As AI models continue to scale, the role of USB4 as a flexible, high-bandwidth edge expansion bus will likely become central to how smartphones handle next-generation workloads.

参考文献

- USB Implementers Forum:USB-IF Announces Publication of New USB4® Specification to Enable USB 80Gbps Performance

- Synopsys:PAM-3 Tech Enhances USB4 v2 Implementation

- Qualcomm:Snapdragon 8 Elite Gen 5 Product Brief

- MediaTek (PR Newswire):MediaTek Dimensity 9500 Unleashes Best-in-Class Performance, AI Experiences, and Power Efficiency

- NotebookCheck:USB4 v2 shows clear gaming performance gains over 40 Gbps USB4 in OneXGPU Lite tests

- Mordor Intelligence:USB Devices Market Size, Share Analysis & Trend Research Report, 2031